Des chercheurs ont développé la première puce 3D monolithique produite entièrement dans une fonderie de semi-conducteurs américaine et offrant des performances supérieures à celles des puces 2D classiques. Constituée de couches de circuits extrêmement fines empilées les unes sur les autres et reliées par des câblages verticaux denses, la puce aurait surmonté la limite fondamentale du « mur de la mémoire » – une exigence essentielle pour satisfaire les besoins croissants de l’IA en matière de puissance de calcul.

Les systèmes d’IA de haut niveau tels que GPT d’OpenAI, Claude d’Anthropic ou encore Gemini de Google, reposent sur la transmission de grands volumes de données entre la mémoire et les unités de calcul. La première se charge du stockage des informations, tandis que les secondes traitent ces informations.

Avec les puces (ou processeurs) 2D standards, la mémoire et les unités de traitement sont disposées au niveau d’un seul plan avec une mémoire locale limitée. Les données doivent donc se déplacer via un petit nombre de circuits à la fois longs et encombrés. Et pour pouvoir transporter les grands volumes de données inhérents à l’IA, des milliers de puces travaillant simultanément sont généralement nécessaires, notamment dans les centres de données dédiés à l’entraînement et à l’exécution de modèles de grande taille.

En effet, si les unités de calcul peuvent fonctionner à très grande vitesse, la mémoire ne suit généralement pas, ce qui entraîne des délais de traitement répétés. Autrement dit, la capacité de calcul dépasse celle du transfert des données – une limitation fondamentale que les ingénieurs surnomment « mur de la mémoire ».

Les ingénieurs ont pendant des décennies tenté de surmonter cette limite en réduisant par exemple la taille des transistors (les petits commutateurs effectuant les calculs) de sorte à pouvoir en intégrer un plus grand nombre sur chaque puce. Cependant, cette approche a, elle aussi, une limite physique connue sous l’appellation de « mur de miniaturisation ».

Une architecture tridimensionnelle pour repenser le lien entre mémoire et calcul

Une étude codirigée par l’Université de Stanford propose une nouvelle puce 3D qui permettrait de surmonter simultanément ces obstacles. Bien que des puces 3D aient précédemment déjà été proposées, il s’agirait de la première à démontrer des gains de performances significatifs par rapport aux puces 2D. « Cela ouvre la voie à une nouvelle ère de production et d’innovation dans le domaine des puces », a déclaré dans un communiqué Subhasish Mitra, professeur titulaire de la chaire William E. Ayer en génie électrique et professeur d’informatique à l’université de Stanford, et auteur principal de l’étude.

« C’est grâce à des avancées comme celle-ci que nous pourrons atteindre des performances matérielles très supérieures à celles d’aujourd’hui », a-t-il ajouté. Les résultats de la recherche ont été présentés à l’occasion de la 71e conférence annuelle de l’IEEE sur les dispositifs électroniques (IEDM).

Contrairement aux puces 2D classiques qui répartissent les composants sur une seule surface plane, la nouvelle puce 3D empile des couches de circuits extrêmement fines les unes sur les autres et reliées par des connexions verticales. Cela permettrait un transfert plus rapide des données entre la mémoire et les unités de calcul.

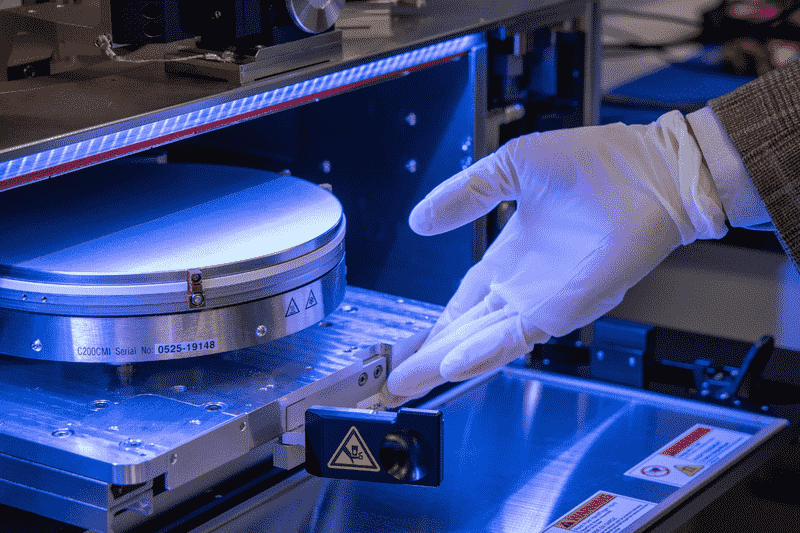

À noter que les précédentes approches de puces 3D reposaient principalement sur des puces entières empilées les unes sur les autres. Cependant, les connexions entre ces puces étaient mal agencées et clairsemées, ce qui entravait leur fonctionnement. En revanche, plutôt que produire des puces séparées pour ensuite les combiner, l’équipe de la nouvelle étude a construit chaque couche de circuit directement sur la précédente en un seul processus continu.

« En intégrant la mémoire et le calcul verticalement, nous pouvons déplacer beaucoup plus d’informations beaucoup plus rapidement, tout comme les ascenseurs d’un immeuble permettent à de nombreux résidents de se déplacer simultanément entre les étages », compare Tathagata Srimani, professeur adjoint de génie électrique et informatique à l’université Carnegie Mellon et coauteur principal de l’étude.

Cette technique de fonderie dite « monolithique » utilise des températures suffisamment basses pour ne pas risquer d’endommager les circuits sous-jacents. Cela permettrait d’empiler des composants plus densément par rapport aux puces 2D et de les connecter de manière plus étroite – surmontant ainsi les deux murs auxquels les puces actuelles se heurtent.

« Le mur de la mémoire et celui de la miniaturisation forment une combinaison redoutable », explique Robert M. Radway, professeur adjoint de génie électrique et des systèmes à l’Université de Pennsylvanie et également co-auteur de l’étude. « Nous l’avons attaqué de front en intégrant étroitement la mémoire et la logique, puis en augmentant considérablement la densité des composants », précise-t-il, avant d’illustrer son propos par une métaphore : « C’est un peu le Manhattan de l’informatique : on peut loger plus de personnes dans moins d’espace. »

Des gains de performance mesurés et un enjeu industriel stratégique

D’après les chercheurs, la nouvelle puce 3D surpasse les puces 2D de niveau équivalent d’un facteur quatre, lors de tests préliminaires. Cela suggère que des versions comprenant davantage de couches empilées pourraient être encore plus performantes. Les modèles comportant des niveaux de circuits supplémentaires auraient montré un gain d’amélioration 12 fois supérieur sur des charges de travail réelles liées à l’IA.

Par ailleurs, l’équipe affirme que la puce pourrait offrir à terme une amélioration du produit énergie-délai (EDP) – un indicateur d’équilibre entre la vitesse et l’efficacité énergétique – d’un facteur 100 à 1000. La réduction du temps de transfert de données permettrait à la puce d’atteindre une vitesse plus élevée pour une faible consommation énergétique.

Un autre avantage est que le processus de fabrication a été réalisé entièrement dans une fonderie de silicium commerciale américaine. « Transformer un concept académique de pointe en un produit commercialisable représente un défi de taille », souligne Mark Nelson, co-auteur de l’étude et vice-président des opérations de développement technologique chez SkyWater Technology.

Les résultats de l’étude constitueraient une démonstration de la faisabilité de la production locale de puces et autres matériels d’IA, contribuant ainsi aux efforts des États-Unis pour la production nationale en la matière et à la réduction de la dépendance envers d’autres puissances étrangères telles que la Chine.